Master Slave JK Flip Flop

1.67M views1417 WordsCopy TextShare

Neso Academy

Digital Electronics: Master Slave JK Flip Flop

Contribute: http://www.nesoacademy.org/donate

Websi...

Video Transcript:

in the last presentation we completed racing or raised around condition in JK flip-flop I explained you how our output is changing in this manner that we call as de racing and racing is definitely not a desired output we don't use Racing in anything so what we use we use toggling and the difference between toggling and racing is that racing is an uncontrolled phenomena whereas the toggling is controlled so we are having some ways by which we can have toggling out of the racing condition the first one that I told you was keeping the clock half

time period that is T by 2 less than the propagation delay of our flip-flop but let me tell you one thing that this particular method to overcome the racing is not practical and it is not used so what we are left with we are left with the second method that is our edge triggering and definitely it is used and the third one and the most important one is the master slave operation that we are going to discuss in this presentation and this master slave operation is same as the negative edge triggering so let me write

this important point so that you may remember this thing the master slave operation is same as negative edge triggered flip-flop I will explain this thing in one of my presentations when we are having our clock and a circuit depending upon some outputs we will see how the negative edge triggered flip-flop is same as our master slave flip-flop it is a very important point to remember and it helps some time to solve the multiple choice question so keep this thing in your mind now let's move to our master slave operation here you can see a JK

flip-flop a simple JK flip-flop is here with the feedbacks and the racing is because of this feedback only so we have to design something so that we can eliminate the effect of this feedback so what we are going to do we have to add another stage by another stage I mean we have to add another socket like this so let's do it it will be clear in a minute so I need to remove this feedback so let's do it first okay now the feedback is removed and we have to add one more stage so I

have already copied it down let me paste it this is our one more stage okay now let us connect the output to the input of the second stage like this and now let us connect the feedback to the output of this stage so what we have done instead of having this input to this gate from here the output of the first stage we have connected the feedback to the output of the second stage so this is important thing in a master-slave flip-flop there are basically two things you have to remember in master-slave flip-flop the first

thing is this feedback that how to connect the feedback and the second important thing is the clock you can see a clock has been given to this stage and also there is a slot for a clock for this stage but instead of having the clock directly given to this stage we will complement it first so we will add a not gate here and now this is the second important point in the master slave operation and this circuit we call as the master slave circuit it can be implemented for s R as well as D flip-flop

there is no problem in doing that but in this presentation we are going to discuss for JK flip-flop so what is the effect of complimenting the clock let's see for example if J is 1 K is 1 and clock is high so what will happen this first stage these are actually the two flip-flops one is my flip-flop one this one is my flip-flop two and this flip-flop I call as the master so let me write it down this flip-flop I call as the master and this flip-flop I called as the slave and because of this

thing only they are called as the master slave now I will explain you why it is called as master and why it is called as slave it all depends upon the clock because when clock is high this master is operational but as the clock is complimented and given to the slave the slave will not be operational it will keep the memory so we are having our output QM changed and the output Q remains the same because the clock is hello when the clock is high for the master similarly when the clock is low the clock

will high for the slave and master will not be functional whereas the slave will be functional and the output changes but there is one interesting thing going on that when this output changes we are having feedback here but the clock is low therefore this master is not operational so there is no effect of feedback we have eliminated the effect of feedback and hence the racing so what actually is happening in this circuit is that instead of output changing continuously from 1 to 0 the output changes once in a clock cycle this is the advantage of

the circuit and that is called as the toggling for better understanding we have to make a clock and we have to see for our outputs Q M and Q so let's make our clock first the clock is changing as a function of time and the values for J and K are 1 throughout okay so this is my clock this is low this is high and c-loc K now we will see what is the value of Q M for this so this is my qm i will extend this line so that we can plot our outputs

in a correct manner so let me do it first okay this much we'll walk now we will plot QM when clock is high it means the master is operational while the slave is not so when the master is operational and I assume that QM was low before the clock is high so as soon as the clock is high the QM will become high also because it was low earlier okay and for for what time it will be high it will be high for this entire time because when the clock becomes low the state will be

stored and the state was high so it will be stored like this and again when the clock is high it will become low like this and then high so you can see that for a clock cycle we are having the toggling okay it is high then it is low this can be used directly now we will try to find out our queue that is the output of our slave and let's see what we are having when the clock is high it means that the master is operational but the slave is not because we are complementing

the clock so here I am having zero so if zero was the output previously I am having zero store till the clock is high and when the clock is low zero here I am having one here it means the slave is operational so it will go high and it will remain high until the clock again became low so low and then high so this is what we are having as the output of our master and output of our slave and you can clearly see that we have overcome this racing the output is not changing continuously

from zero to one but it is changing once in a cycle that's we call as the toggling so if I write the value for our output when J and K and our clock is high the output Q and plus one will be Q and complement this we call as the toggling and it is used in the counters so I hope you understand now what is master slave operation in JK flip-flop it's a very simple thing you can also do it for the D flip-flop and this is all for this presentation in the next presentation we

will try to understand the operation of the T flip-flop so see you in the next one

Related Videos

11:48

Behaviour of Master Slave D Flip Flop

Neso Academy

761,445 views

8:58

Race Around Condition or Racing in JK Flip...

Neso Academy

1,338,769 views

12:27

S-R Flip Flop

TutorialsPoint

942,714 views

8:56

Truth Table, Characteristic Table and Exci...

Neso Academy

2,038,009 views

10:05

Master Slave JK Flip Flop: Circuit, Workin...

Engineering Funda

140,797 views

18:48

Master Slave JK Flip-Flop Explained | Digi...

ALL ABOUT ELECTRONICS

62,081 views

7:46

Introduction to JK flip flop

Neso Academy

2,636,754 views

32:58

JK Flip Flop - Basic Introduction

The Organic Chemistry Tutor

131,772 views

11:40

Introduction to Counters | Important

Neso Academy

2,164,837 views

13:49

Latches and Flip-Flops 6 - The JK Flip Flop

Computer Science

33,291 views

6:58

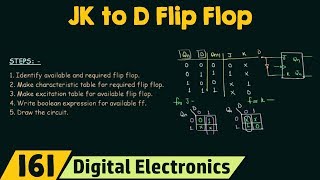

5 Steps for Flip Flop Conversions | JK to ...

Neso Academy

1,206,152 views

10:03

JK flip-flop

Ben Eater

551,645 views

8:23

Introduction to SR Flip Flop

Neso Academy

3,285,070 views

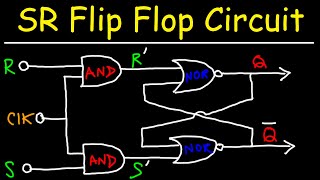

13:59

SR Flip Flop Circuit With NAND and NOR Gates

The Organic Chemistry Tutor

78,932 views

6:33

JK Flip Flop Timing Diagrams

Joe Haas

185,389 views

4:38

Master Slave JK Flip-Flop.

Engg-Course-Made-Easy

5,167 views

10:59

Master Slave JK Flip Flop | Digital Electr...

Gate Smashers

529,435 views

22:23

Module3_Class5_Master slave JK flipflop

shilpa V

24,915 views

4:35

Introduction to D flip flop

Neso Academy

2,201,338 views